Entwicklung

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

local x = {} local n = 2 while true do for i = 1, n do x[i] = i .. i -- Make a string end n = n + n // 2 collectgarbage() print('-------->', n, collectgarbage('count')) x = nil collectgarbage() x = {} if n >= 18207 then n = 2 end end |

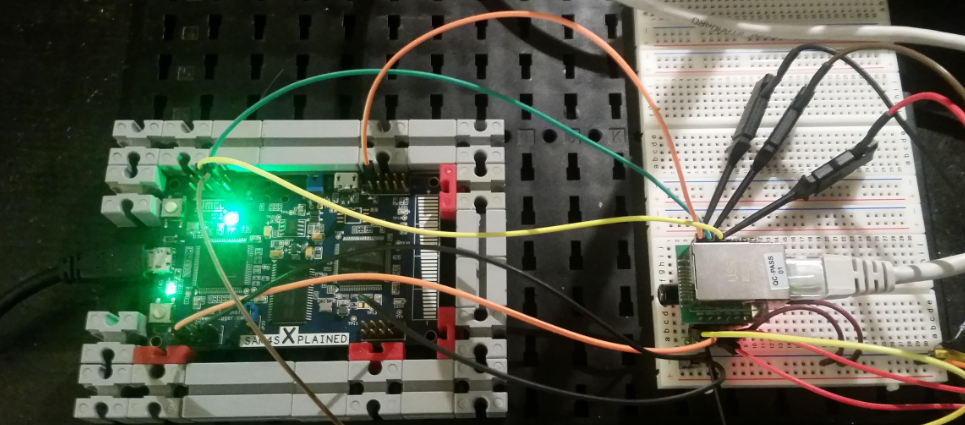

Nach einem erfolgreichen Test des Speichers kam die Generalprobe: sunfish Schach. Damit das Program akzeptabel schnell läuft habe ich noch folgedes angepasst:

|

1 2 3 4 5 |

-- The table size is the maximum number of elements in the transposition table. local TABLE_SIZE = 1e4 --1e6 -- This constant controls how much time we spend on looking for optimal moves. local NODES_SEARCHED = 1e2 --1e4 |

Die Orginalwerte sind in den Kommentaren erhalten geblieben.

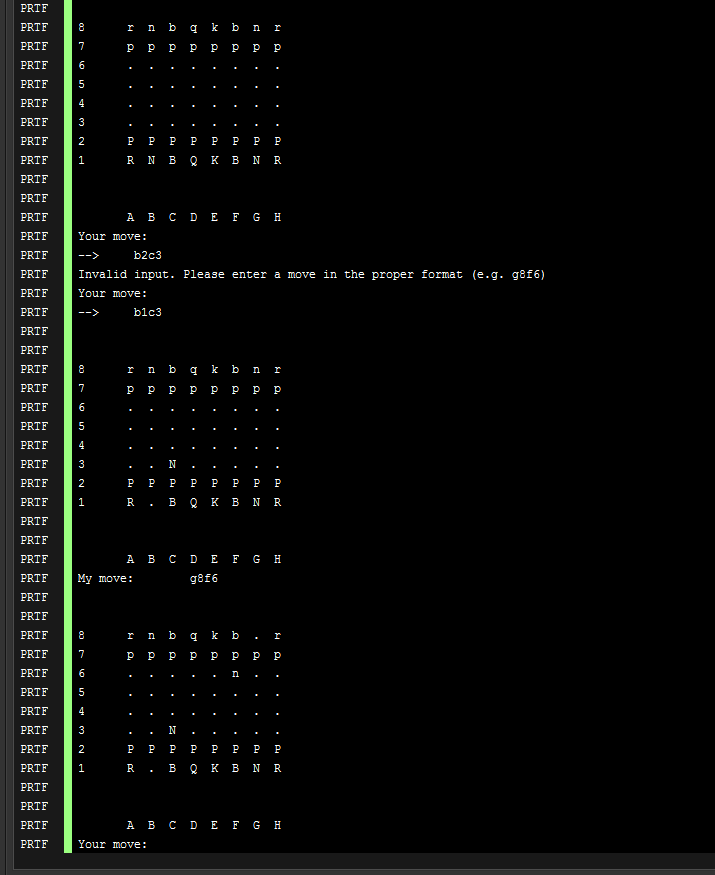

Für den Test habe ich die Ausgabe mit der NOGS-ID angezeigt, ein SysLog Tool wäre auch geeignet gewesen. Für die Eingabe der Züge habe ich die Debug Konsole von Cross-Studio verwendet.

Und hier sind die ersten Züge zu sehen, die CN2 in spe spielt schwarz.

Hardware

Technische Daten:

| Size | 56 x 38 mm, Pins Breadboard compatible |

| Processor | Atmel ARM Cortex M4, ATSAM4S16C |

| Clock Speed | 120 MHz |

| RAM | 160 KB + 1MB |

| Flash | 1024 KB |

| Storage | microSD, FFS (Far File System, FlashFS (read only). All with VFAT32 |

| Encryption | Atmel, 256 bit Random Number Generator, 72 bit Serial Number, 512 bit OTP Memory, SHA-256 Hash Algorithm, ATSHA204A |

| Input Voltage | 5 V |

| Power | 150 mA (0,75 W) |

| Digital GPIO | 26 |

| Analog Input | 10 (10-bit) |

| PWM | 3 |

| TWI / I2C | 1 |

| SPI | 1 |

| UART | 4 (1x USART, 3x UART) |

| RTOS | Nogs Clever Node |

| Dev-IDE | Nogs IDE with Lua Live Coding, ZeroBrane Studio |

| Ethernet | 10 M / 100 M, WIZnet W5500 |

| USB Master | Option via Pin |

| Video Output | FTDI EVE Option |

| Audio Output | FTDI EVE Option |

Die vorläufige Pinbelegung ist hier zu finden: CN2 Pinout.

Die Belegung der CPU Pins für CN1 und CN2 ist hier zu finden: Pins CN1 CN2

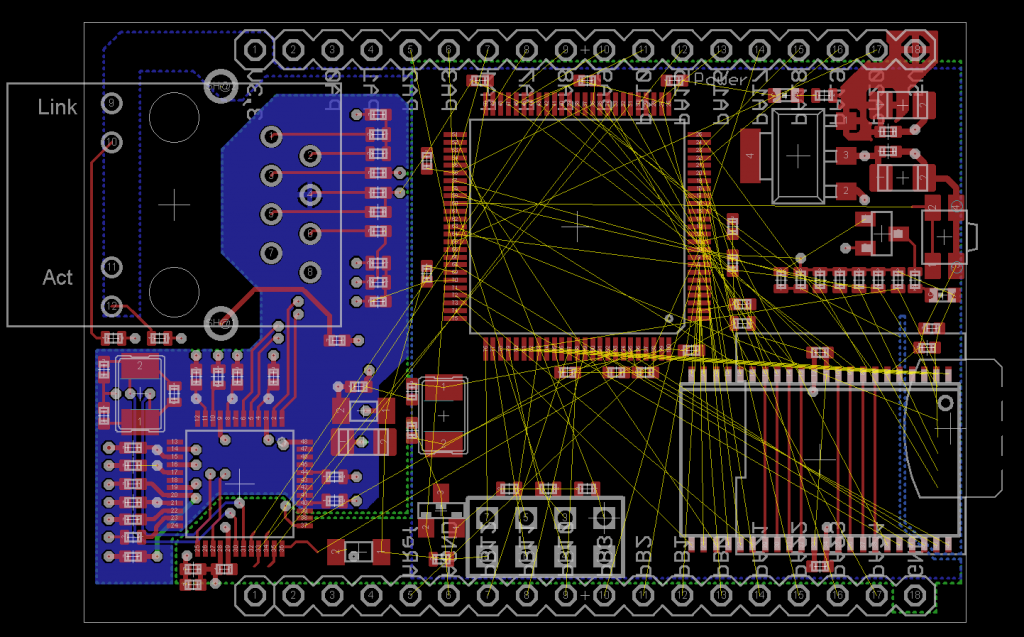

Bauteilanordnung

Die µSD-Card is auf die Rückseite der Platine gewandert. Die größere CPU und der Speicher scheinen auf das Board zu passen. Die Herausforderung ist die Leiterbahnführung…

Nächste Schritte

Als nächstes muss die CN1 Platine zur CN2 werden. Da die neue CPU und der Speicher mehr Platz benötigen muss entschieden werden ob die Platine doppelseitig bestückt wird oder ob BGA Gehäuse für CPU und/oder Speicher verendet werden.

Verlegen der Leiterbahnen.